# SSD2677

# **Product Information**

960 Source x 680 Gate **Active Matrix EPD Display Driver with Controller** for color application

This document contains information on a product under definition stage. Solomon Systech reserves the right to change or discontinue this product without notice. http://www.solomon-systech.com

SSD2677 products shall only be used solely with Permitted E5 Spectra 3100 FPL licensed by E Ink, customer should notify the same acknowledgement with its downstream customers. SSD2677

Aug 2023

P 1/19

Rev 1.1

Product Info

### 1 Features

- On chip display RAM

- On-chip booster and regulator for generating VCOM, Gate and Source driving voltage

- 680 outputs gate driver, 960 outputs source driver, 1 output VBD driver for border

- On-chip oscillator

- Embedded OTP to store the waveform settings and parameters

- Support low voltage detect for supply voltage

- Internal Temperature Sensor

- MCU interface: Serial peripheral (3-wire/4-wire)

- · Available in COG package

### 2 ORDERING INFORMATION

**Table 2-1: Ordering Information**

| Ordering Part Number | Package Form  | Remark                                                               |

|----------------------|---------------|----------------------------------------------------------------------|

| SSD2677ZB            | Gold Bump Die | Bump Face Down On Waffle pack Die thickness: 300um Bump height: 12um |

| SSD2677ZC            | Gold Bump Die | Bump Face Up On Waffle pack Die thickness: 300um Bump height: 12um   |

SSD2677 products shall only be used solely with Permitted E5 Spectra 3100 FPL licensed by E Ink, customer should notify the same acknowledgement with its downstream customers.

SSD2677 Product Info

Rev 1.1

P 2/19

Aug 2023

Solomon Systech

## 3 Pin Description

$\begin{tabular}{ll} \textbf{Key:} & I = Input, O = Output, IO = Bi-directional (input/output), P = Power pin, C = Capacitor Pin NC = Not Connected, Pull L = connect to GND, Pull H = connect to <math>V_{DDIO}$

Table 3-1: Pin list for SSD2677

| Name      | Type | Connect to                    | Description                              | When not in use |

|-----------|------|-------------------------------|------------------------------------------|-----------------|

| VDD       | Р    | Power Supply                  | Power Supply pin for the chip            | -               |

| VDDIO     | Р    | Power Supply                  | Power for interface logic pins           | -               |

| VCORE     | С    | Capacitor                     | Core logic power regulator output pin    |                 |

| VCORE1    | С    | Capacitor                     | Core logic power pin                     | -               |

| GND       | P    | GND                           | Ground                                   | -               |

| GNDA      | P    | GND                           | Ground                                   | -               |

| VPP       | P    | Reserved                      | Reserved                                 | Open            |

| SCL       | i    | MPU                           | Serial clock pin (SPI)                   | -               |

| SDA       | I/O  | MPU                           | Serial data pin (SPI)                    | -               |

| CSB       | ı, O | MPU                           | Chip Select input pin                    | _               |

| DC        | i    | MPU                           | Data /Command control pin                | VDDIO or GND    |

| RST_N     | i    | MPU                           | Reset                                    | -               |

| BUSY_N    | 0    | MPU                           | Busy state output pin                    | -               |

| BS1       | Ī    | VDDIO/GND                     | Interface Selection Pin                  | -               |

| M/S#      | i    | Reserved                      | Tie to VDDIO.                            | -               |

| TPE       | I/O  | Reserved                      | Connect to TPE                           | -               |

| TIN       | I/O  | Reserved                      | Connect to TIN                           | -               |

| GDR       | I/O  | Analog Pin                    | N-Channel MOSFET Gate Drive Control      | _               |

| RESE      | I/O  | Analog Pin                    | Current Sense Input for the Control Loop | -               |

| VGH       | C    | Stabilizing capacitor         | Power Supply pin for VSH                 | -               |

| VGL       | C    | Stabilizing capacitor         | Power Supply pin for VCOM and VSL        | -               |

| VSH1      | С    | Stabilizing capacitor         | Positive Source driving voltage          | -               |

| VSH2      | С    | Stabilizing capacitor         | Positive Source driving voltage          | -               |

| VSL       | С    | Stabilizing capacitor         | Negative Source driving voltage          | -               |

| VCOM      | C    | Panel & Stabilizing capacitor | VCOM driving voltage                     | -               |

| S [959:0] | 0    | Panel                         | Source output pin.                       | Open            |

| G [679:0] | 0    | Panel                         | Gate output pin.                         | Open            |

| VBD       | 0    | Panel                         | Border output pin.                       | Open            |

| TSCL      | 0    | Reserved                      | Reserved                                 | VSS             |

| TSDA      | I/O  | Reserved                      | Reserved                                 | VSS             |

| SYNC0     | I/O  | Reserved                      | Reserved                                 | Open            |

| SYNC1     | I/O  | Reserved                      | Reserved                                 | Open            |

| CL        | NC   | NC                            | Reserved                                 | Open            |

| RSV       | NC   | NC                            | Reserved                                 | Open            |

| TP1       | NC   | NC                            | Test Pin                                 | Open            |

| TP2       | NC   | NC                            | Test Pin                                 | Open            |

| TP3       | NC   | NC                            | Test Pin                                 | Open            |

| TP4       | NC   | NC                            | Test Pin                                 | Open            |

| TP5       | NC   | NC                            | Test Pin                                 | Open            |

| TP6       | NC   | NC                            | Test Pin                                 | Open            |

| TP7       | NC   | NC                            | Test Pin                                 | Open            |

| TP8       | NC   | NC                            | Test Pin                                 | Open            |

| TP9       | NC   | NC                            | Test Pin                                 | Open            |

| FB        | NC   | NC                            | Test Pin                                 | Open            |

SSD2677 products shall only be used solely with Permitted E5 Spectra 3100 FPL licensed by E lnk, customer should notify the same acknowledgement with its downstream customers.

SSD2677 Product Info

Rev 1.1

P 3/19

Aug 2023

Solomon Systech

### 4 MCU Interface

#### 4.1 MCU Interface selection

The SSD2677 can support 3-wire/4-wire serial peripheral. In the SSD2677, the MCU interface is pin selectable by BS1 shown in Table 4-1.

#### Note

- (1) L is connected to GND

- (2) H is connected to V<sub>DDIO</sub>

Table 4-1: Interface pins assignment under different MCU interface

| MCU Interface                                         | BS1 | RST_N    | CSB | DC | SCL | SDA |

|-------------------------------------------------------|-----|----------|-----|----|-----|-----|

| 4-wire serial peripheral interface (SPI)              | L   | Required | CSB | DC | SCL | SDA |

| 3-wire serial peripheral interface (SPI) – 9 bits SPI | Н   | Required | CSB | L  | SCL | SDA |

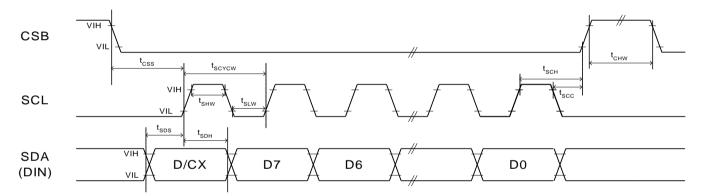

### 4.2 MCU Serial Interface (4-wire SPI)

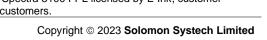

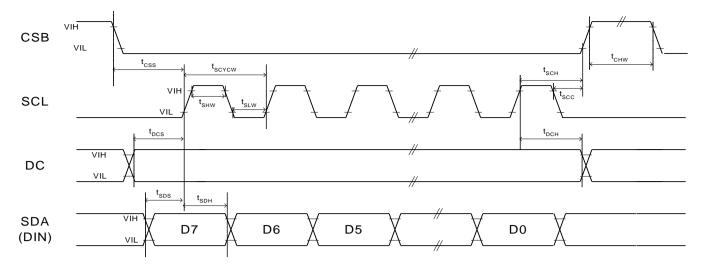

The 4-wire SPI consists of serial clock SCL, serial data SDA, DC and CSB. The control pins status in 4-wire SPI in reading/writing command/data is shown in

Table 4-2. The read/write procedure of 4-wire SPI is shown in Figure 4-1.

Table 4-2: Control pins status of 4-wire SPI

| Function        | SCL pin | SDA pin     | DC pin | CSB pin |

|-----------------|---------|-------------|--------|---------|

| Write command   | 1       | Command bit | L      | L       |

| Read/Write data | 1       | Data bit    | Н      | L       |

#### Note:

- (1) L is connected to GND and H is connected to  $V_{\text{DDIO}}$

- (2) ↑ stands for rising edge of signal

- (3) SDA (Write Mode) is shifted into an 8-bit shift register on every rising edge of SCL in the order of D7, D6, ... D0. The level of DC should be kept over the whole byte. The data byte in the shift register is written to the Graphic Display Data RAM (RAM)/Data Byte register or command Byte register according to DC pin.

Figure 4-1: Read/Write procedure in 4-wire SPI mode

SSD2677 products shall only be used solely with Permitted E5 Spectra 3100 FPL licensed by E Ink, customer should notify the same acknowledgement with its downstream customers.

SSD2677 Product Info

Rev 1.1

P 4/19

Aug 2023

Solomon Systech

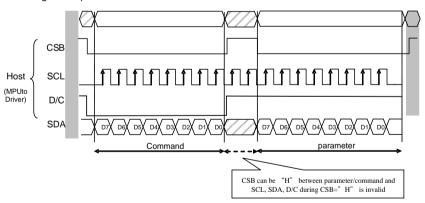

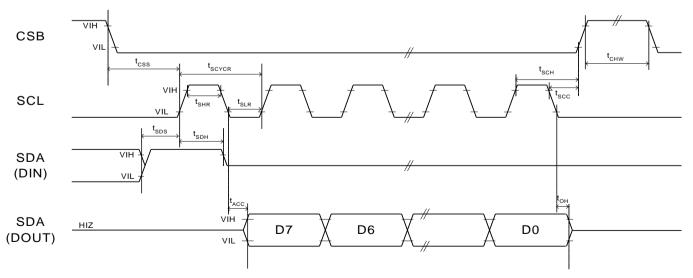

### 4.3 MCU Serial Peripheral Interface (3-wire SPI)

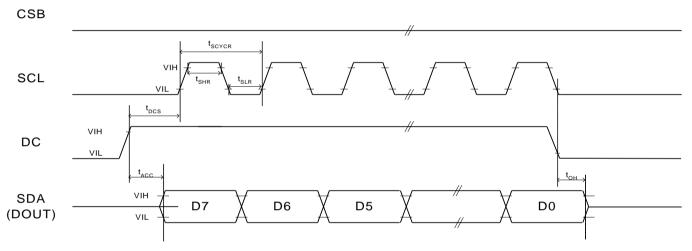

The 3-wire SPI consists of serial clock SCL, serial data SDA and CSB. The operation is similar to 4-wire SPI while DC pin is not used and it must be tied to LOW. The control pins status in 3-wire SPI is shown in Table 4-3. The read/write procedure of 3-wire SPI is shown in Figure 4-2.

In the read/write operation, a 9-bit data will be shifted into the shift register on every clock rising edge. The bit shifting sequence is DC bit, D7 bit, D6 bit to D0 bit. The first bit is DC bit which determines the following byte is command or data. When DC bit is 0, the following byte is command. When DC bit is 1, the following byte is data. Table 4-3 shows the write procedure in 3-wire SPI

Table 4-3: Control pins status of 3-wire SPI

| Function        | SCL pin | SDA pin     | DC pin  | CSB pin |

|-----------------|---------|-------------|---------|---------|

| Write command   | 1       | Command bit | Tie LOW | L       |

| Read/Write data | 1       | Data bit    | Tie LOW | L       |

#### Note:

- (1) L is connected to GND and H is connected to V<sub>DDIO</sub>

- (2) ↑ stands for rising edge of signal

Figure 4-2: Read/Write procedure in 3-wire SPI mode

SSD2677 products shall only be used solely with Permitted E5 Spectra 3100 FPL licensed by E Ink, customer should notify the same acknowledgement with its downstream customers.

SSD2677 Product Info

Rev 1.1

P 5/19

Aug 2023

Solomon Systech

# 5 Command Table Description

| _    | <del></del> | 111116 |                | . 4.5          |                       | -              |                       | <u> </u>       |                       |                | 1       |                                                                                                               |

|------|-------------|--------|----------------|----------------|-----------------------|----------------|-----------------------|----------------|-----------------------|----------------|---------|---------------------------------------------------------------------------------------------------------------|

| R/W# | DC          | Hex    | D7             | D6             | D5                    | D4             | D3                    | D2             | D1                    | D0             | Command | Description                                                                                                   |

| 0    | 0           | 00     | 0              | 0              | 0                     | 0              | 0                     | 0              | 0                     | 0              | PSR     | Panel Setting Register                                                                                        |

| 0    | 1           |        | A <sub>7</sub> | A <sub>6</sub> | <b>A</b> <sub>5</sub> | 0              | <b>A</b> <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub>        | A <sub>0</sub> |         | A[7:0] = 0Fh [POR]                                                                                            |

|      |             |        | / (/           | 710            | 713                   |                | 713                   | / 1/2          | 7 (1                  | / 10           |         | B[7:0] = 09h [POR]                                                                                            |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | A[7:6] ~ RES[1:0]                                                                                             |

| 0    | 1           |        | B <sub>7</sub> | $B_6$          | B <sub>5</sub>        | B <sub>4</sub> | $B_3$                 | B <sub>2</sub> | B₁                    | B <sub>0</sub> |         | Display Resolution setting (source x gate) 00b: 960 x 680 (Default)                                           |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 01b: 960 x 672                                                                                                |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 10b: 960 x 640                                                                                                |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 11b: 880 x 528                                                                                                |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | A[3] ~ UD                                                                                                     |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | Gate Scan Direction:                                                                                          |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 0: Scan down.                                                                                                 |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | First line to Last line: Gn-1 G0                                                                              |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 1: Scan up. (Default)                                                                                         |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | First line to Last line: G0 Gn-1                                                                              |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | A[2] ~ SHL                                                                                                    |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | Source Shift Direction:                                                                                       |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 0: Shift left.                                                                                                |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | First data to Last data: Sn-1 S0 1: Shift right. (Default)                                                    |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | First data to Last data: S0 Sn-1                                                                              |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | A[1] ~ SHD_N                                                                                                  |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | Booster and Regulator Switch:                                                                                 |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 0: PON / POF command will not execute                                                                         |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 1: PON / POF command will execute (Default)                                                                   |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | A[0] ~ RST_N                                                                                                  |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | Soft Reset:                                                                                                   |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 0: The controller is reset. Reset all registers to their default value. Driver all function will be disabled. |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 1: Normal operation (Default).                                                                                |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | BUSY_N signal will become "0" until Soft reset is finished.                                                   |

|      |             |        |                |                |                       |                |                       |                |                       |                |         |                                                                                                               |

| 0    | 0           | 01     | 0              | 0              | 0                     | 0              | 0                     | 0              | 0                     | 1              | PWR     | Power setting Register                                                                                        |

|      |             |        | 5              |                |                       |                |                       |                |                       | '              |         | A[5:0] = 07h [POR]                                                                                            |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | B[7:0] = F0h [POR]                                                                                            |

| 0    | 1           |        | 0              | 0              | 0                     | 0              | 0                     | A <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub> |         | A[2:0] = 111 [POR]                                                                                            |

| 0    | 1           |        | 1              | 1              | 1                     | 1              | 0                     | 0              | B₁                    | B <sub>0</sub> |         | B[1:0] ~ VGPN [1:0]                                                                                           |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | Internal VGH / VGL Voltage Level Selection:                                                                   |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | VGPN [1:0] Gate Voltage Level  00 VGH=20V,VGL=-20V (Default)                                                  |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 00 VGH=20V,VGL=-20V (Default)<br>VSH=15V, VSL=-15V                                                            |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 01 VGH=17V ,VGL=-17V                                                                                          |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | VSH=15V, VSL=-15V                                                                                             |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 10 VGH=15V,VGL=-15V                                                                                           |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | VSH=15V, VSL=-15V                                                                                             |

|      |             |        |                |                |                       |                |                       |                |                       |                |         | 11 Reserved.                                                                                                  |

|      |             |        |                |                |                       |                |                       |                |                       | <u> </u>       | 1       |                                                                                                               |

| SSD2677      | Pov. 1.1 | P 6/19 | Aug 2023 | Salaman Systach |

|--------------|----------|--------|----------|-----------------|

| Product Info | Rev 1.1  | P 6/19 | Aug 2023 | Solomon Systech |

| R/W# | DC | Hex | D7 | D6             | D5                    | D4             | D3                    | D2             | D1             | D0             | Command | Description                                                                                                                                                                                                                                                                                                                                               |

|------|----|-----|----|----------------|-----------------------|----------------|-----------------------|----------------|----------------|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0  | 02  | 0  | 0              | 0                     | 0              | 0                     | 0              | 1              | 0              | POF     | Power OFF Command Register                                                                                                                                                                                                                                                                                                                                |

| 0    | 1  |     | 0  | 0              | 0                     | 0              | 0                     | 0              | 0              | 0              |         | After power off command, driver will power off based on the Power OFF Sequence, then BUSY_N signal will become "0".  The Power OFF command will turn off DCDC, source driver, gate driver, VCOM driver, temperature sensor, but register and SRAM data will keep until VDD off. SD output will base on previous condition. *Remark: POF works at PON only |

| 0    | 0  | 04  | 0  | 0              | 0                     | 0              | 0                     | 1              | 0              | 0              | PON     | Power ON Command Register After the Power ON command, driver will power on based on the Power ON Sequence. After power on command and all power sequence are ready, then BUSY_N signal will become "1".  * Remark: PON Include booster on, VSHx/VSLx regulator on With default BTST, timing is >80ms                                                      |

| 0    | 0  | 06  | 0  | 0              | 0                     | 0              | 0                     | 1              | 1              | 0              | BTST    | VGH Booster Soft Start Setting Register (for VGH)                                                                                                                                                                                                                                                                                                         |

| 0    | 1  |     | 0  | 0              | 0                     | 0              | <b>A</b> <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |         | A[6:0] = 0Fh [POR]                                                                                                                                                                                                                                                                                                                                        |

| 0    | 1  |     | 1  | B <sub>6</sub> | <b>B</b> <sub>5</sub> | B <sub>4</sub> | Вз                    | B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> |         | B[6:0] = 8Bh [POR]<br>C[6:0] = 93h [POR]                                                                                                                                                                                                                                                                                                                  |

| 0    | 1  |     | 1  | C <sub>6</sub> | <b>C</b> <sub>5</sub> | C <sub>4</sub> | <b>C</b> <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | Co             | -       | D[6:0] = 93ft [POR]                                                                                                                                                                                                                                                                                                                                       |

| 0    | 1  |     | 1  | D <sub>6</sub> | D <sub>5</sub>        | D <sub>4</sub> | D <sub>3</sub>        | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |         | A[3:2] ~ T_VGHSSA [1:0] = 11 (Default) VGH booster soft start Phase A duration A[1:0] ~ T_VGHSSB [1:0] = 11 (Default) VGH booster soft start Phase B duration  Soft Start Phase Period (ms)  00                                                                                                                                                           |

SSD2677 Product Info

Rev 1.1

P 7/19

Aug 2023

Solomon Systech

| R/W# | DC | Hex | D7                | D6             | D5                 | D4             | D3             | D2             | D1             | D0                | Command | Description                                                                                                                                                                                                                                                                                                            |

|------|----|-----|-------------------|----------------|--------------------|----------------|----------------|----------------|----------------|-------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0  | 07  | 0                 | 0              | 0                  | 0              | 0              | 1              | 0              | 1                 |         | Deep Sleep Register This command makes the chip enter the deep-sleep mode. The deep sleep mode could return to stand-by mode by hardware reset assertion. The only one parameter is a check code, the command would be executed if check code is A5h.                                                                  |

| 0    | 0  | 17  | 0                 | 0              | 0                  | 1              | 0              | 1              | 1              | 1                 | AUTO    | Auto Sequence Register                                                                                                                                                                                                                                                                                                 |

| 0    | 1  |     | A <sub>7</sub>    | A <sub>6</sub> | A <sub>5</sub>     | A <sub>4</sub> | Аз             | A <sub>2</sub> | A <sub>1</sub> | Ao                |         | This command makes the chip enter the auto sequence Single-chip application ONLY. Auto Sequence Option 0xA5: Start Auto Sequence (PON > DRF > POF) 0xA7: Start Auto Sequence (PON > DRF > POF > DSLP). Others: No effect BUSY_N signal will become "0" until Auto Sequence is finished.                                |

| 0    | 0  | 10  | 0                 | 0              | 0                  | 1              | 0              | 0              | 0              | 0                 | DTM     | Data Start transmission Register                                                                                                                                                                                                                                                                                       |

| 0    | 1  |     | KPix              | xel1           | per<br>KPix<br>[1: | kel2           | KPiz           |                |                | xel4<br>:0]       |         | This command indicates that user starts to transmit data. Then write to SRAM. While complete data transmission, user must send a Data Refresh command (R12H). Then the chip will start to send data/VCOM for panel.                                                                                                    |

| 0    | 1  |     | KPi<br>(4N<br>[1: | 1-3)           | (4N<br>[1:         | 1-2)           | (4N<br>[1:     |                | (4             | ixel<br>M)<br>:0] |         | KPixel[1:0] Source Driver Output  DDX=1 (Default)                                                                                                                                                                                                                                                                      |

|      |    |     |                   |                |                    |                |                |                |                |                   |         | 00b Gray 0 01b Gray 1 10b Gray 2 11b Gray 3  After issue this command, the host must send at least 1 byte data to the device.                                                                                                                                                                                          |

| 0    | 0  | 12  | 0                 | 0              | 0                  | 1              | 0              | 0              | 1              | 0                 | DRF     | Display Refresh Command Register                                                                                                                                                                                                                                                                                       |

| 0    | 1  |     | 0                 | 0              | 0                  | 0              | 0              | 0              | 0              | 0                 |         | After this command is issued, driver will refresh display (data/VCOM) according to SRAM data and LUT. LUT can define DCVCOM/ACVCOM.  After Display Refresh command, BUSY_N signal will become "0" until display update is finished.                                                                                    |

| 0    | 0  | 40  | 0                 | 1              | 0                  | 0              | 0              | 0              | 0              | 0                 | TSC     | Temperature Sensor Command Register                                                                                                                                                                                                                                                                                    |

| 1    | 1  |     | A <sub>7</sub>    | A <sub>6</sub> | A <sub>5</sub>     | A4             | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | Ao                |         | This command enables internal temperature sensor.  BUSY_N will go low during temperature sensor is under operation. Then the temperature value can be read in 1degC step  A[7:0] ~ TS [7:0]  TS [7:0] Return Value(degC)  E7h -25  FFh -1  00h 0  01h 1  19h 25  31h 49 32h 50  PFL licensed by E Ink. customer should |

SSD2677

Rev 1.1

P 8/19

Aug 2023

Solomon Systech

| R/W# | DC | Hex | D7             | D6                    | D5                    | D4                    | D3                    | D2             | D1                    | D0             | Command | Description                                                                                                                                                                                                                                                                                                        |

|------|----|-----|----------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0  | 50  | 0              | 1                     | 0                     | 1                     | 0                     | 0              | 0                     | 0              | CDI     | A[7:0] = 97h [POR]                                                                                                                                                                                                                                                                                                 |

| 0    | 1  |     | A <sub>7</sub> | A <sub>6</sub>        | A <sub>5</sub>        | 0                     | 0                     | 0              | 0                     | 0              |         | A[7:5]~VBD [2:0] Border Output Selection:    DDX=1     VBD[2:0]   LUT (Default)     000   Gray 0     001   Gray 1     010   Gray 2     011   Gray 3     100   HIZ(Default)                                                                                                                                         |

| 0    | 0  | 61  | 0              | 1                     | 1                     | 0                     | 0                     | 0              | 0                     | 1              | TRES    | Resolution setting Register This command defines alternative resolution                                                                                                                                                                                                                                            |

| 0    | 1  |     | 0              | 0                     | 0                     | 0                     | 0                     | 0              | <b>A</b> 9            | A <sub>8</sub> | -       | A[7:0] ~ HRES[9:0]                                                                                                                                                                                                                                                                                                 |

| 0    | 1  |     | A <sub>7</sub> | A <sub>6</sub>        | A <sub>5</sub>        | A <sub>4</sub>        | A <sub>3</sub>        | A <sub>2</sub> | A <sub>1</sub>        | A <sub>0</sub> |         | Horizontal Display Resolution                                                                                                                                                                                                                                                                                      |

| 0    | 1  |     | 0              | 0                     | 0                     | 0                     | 0                     | 0              | B <sub>9</sub>        | B <sub>8</sub> | -       | Remark: Horizontal resolution should be 4-multiple.                                                                                                                                                                                                                                                                |

| 0    | 1  |     | B <sub>7</sub> | B <sub>6</sub>        | B <sub>5</sub>        | B <sub>4</sub>        | B <sub>3</sub>        | B <sub>2</sub> | B <sub>1</sub>        | B <sub>0</sub> | -       | B[8:0] ~ VRES[9:0]<br>Vertical Display Resolution                                                                                                                                                                                                                                                                  |

|      |    |     |                |                       |                       |                       |                       |                |                       |                |         | e.g. HRES= 3C0h, VRES= 2A8h  UD,SHL Source and gate sequence  00 S679,G959 to S0,G0  01 S0, G959 to S679,G0  10 S679,G0 to S0, G959  11 S0,G0 to S679, G295  Remark: 1) Both PSR.RES & TRES command can set panel resolution. Priority will be given to the last received PSR or TRES command. 2) VRES[8:0] >= 120 |

| 0    | 0  | 70  | 0              | 1                     | 1                     | 1                     | 0                     | 0              | 0                     | 0              | REV     | Chip Revision Register                                                                                                                                                                                                                                                                                             |

| 1    | 1  |     | A <sub>7</sub> | <b>A</b> <sub>6</sub> | <b>A</b> <sub>5</sub> | <b>A</b> <sub>4</sub> | <b>A</b> <sub>3</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub> |         | The command is to read the ID<br>A[7:0] = 07h [POR]                                                                                                                                                                                                                                                                |

SSD2677 Product Info

Rev 1.1

P 9/19

Aug 2023

Solomon Systech

| R/W# | DC | Hex | D7             | D6             | D5         | D4             | D3             | D2             | D1             | D0             | Command | Description                                                                                                                                                                                                                                                                                                                                                                       |

|------|----|-----|----------------|----------------|------------|----------------|----------------|----------------|----------------|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0  | 80  | 1              | 0              | 0          | 0              | 0              | 0              | 0              | 0              | AMV     | Auto Measurement VCOM Register This command implements related VCOM sensing setting. A[7:0] = 00h [POR]                                                                                                                                                                                                                                                                           |

| 0    | 1  |     | A <sub>7</sub> | A <sub>6</sub> | A5         | A <sub>4</sub> | 0              | 0              | 0              | Ao             |         | A[7:6] ~ P[1:0] Number of sensing Points 00: 2 (Default) 01: 4 10: 8 11: 16  A[5:4] ~AMVT[1:0] Auto Measure Vcom Time: Sensing Time 00: 5 sec. (Default) 01: 10 sec. 10: 15 sec. 11: 20 sec.  A[0] ~ AMVE Auto Measure Vcom Enable (/Disable): 0: Disabled (Default) 1: Enabled Requirement:                                                                                      |

|      | 0  | 81  | 1              | 0              | 0          | 0              | _              |                | 0              | 1              | VV      | Auto Measurement VCOM Register                                                                                                                                                                                                                                                                                                                                                    |

| 0    | 0  | 01  | 1              | U              | 0          | U              | 0              | 0              | U              | 1              | VV      | This command gets the Vcom value after AMV.                                                                                                                                                                                                                                                                                                                                       |

| 1    | 1  |     | 1              | 0              | <b>A</b> 5 | A4             | А3             | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> |         | A[5:0] ~ VV[5:0]:         Vcom read Value , valid range from -0.2V to -4.0V.         VV[5:0]       Vcom read value         00h       Reserved         04h       -0.2V         08h       -0.4V         0Ch       -0.6V         10h       -0.8V             50h       -4.0V         others       Reserved                                                                           |

| 0    | 0  | 82  | 1              | 0              | 0          | 0              | 0              | 0              | 1              | 0              | VDCS    | VCM_DC Setting Register                                                                                                                                                                                                                                                                                                                                                           |

|      |    |     |                |                |            |                |                |                |                |                |         | This command sets VCOM_DC value. A[7:0] = 00h [POR]                                                                                                                                                                                                                                                                                                                               |

| 0    | 1  |     | Α <sub>7</sub> | A <sub>6</sub> | <b>A</b> 5 | A4             | A <sub>3</sub> | A <sub>2</sub> | 0              | 0              |         | A[7] ~ OTP_VCM Vcom follow VDCS after RESET.  0: Disable (Default), auto load from OTP if it is valid.  1: Enable, VCOM value from the VDCS[6:0] A[6:0] ~ VDCS[6:0]: VCOM_DC Setting, 0.2V step from -0.2V to -4.0V.  VDCS [6:0] VCOM_DC Setting  00h Reserved  04h -0.2V  08h -0.4V  0Ch -0.6V  10h -0.8V   50h -4.0V  others Reserved  0 FPL licensed by E lnk, customer should |

SSD2677 Product Info

Rev 1.1

P 10/19

Aug 2023

Solomon Systech

| R/W# | DC | Hex | D7                  | D6                                                           | D5                  | D4                  | D3                  | D2                  | D1                  | D0                  | Command | Description                                                                                                                                                                                                                                                                         |

|------|----|-----|---------------------|--------------------------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |    |     |                     |                                                              |                     |                     |                     |                     |                     |                     |         |                                                                                                                                                                                                                                                                                     |

| 0    | 0  | 90  | 1                   | 0                                                            | 0                   | 1                   | 0                   | 0                   | 0                   | 0                   | PGM     | Program Mode This command is to set OTP program mode After this command is issued, the chip would enter the program mode. After the programming procedure completed, a hardware reset is necessary for leave the program mode  BUSY_N signal will become 0 until PGM mode is ready. |

|      |    | ı   |                     |                                                              | 1                   |                     | 1                   | 1                   |                     |                     |         |                                                                                                                                                                                                                                                                                     |

| 0    | 0  | 91  | 1                   | 0                                                            | 0                   | 1                   | 0                   | 0                   | 0                   | 1                   | APG     | Active Program This command is to execute OTP program After this command is issued, the chip would program the OTP. BUSY_N signal will become 0 until the programming is completed. Requirement: In PON mode with internal programming power.                                       |

| 0    | 0  | 92  | 1                   | 0                                                            | 0                   | 1                   | 0                   | 0                   | 1                   | 0                   | ROTP    | Read OTP Data                                                                                                                                                                                                                                                                       |

| 1    | 1  | 92  | ı                   | U                                                            | L Č                 | -                   | _                   | L Č                 | ı                   | U                   | ROTP    | This command is to read the OTP content from SRAM.                                                                                                                                                                                                                                  |

| •    | •  |     |                     | 1 <sup>st</sup> ~ dummy<br>2 <sup>nd</sup> ~ N+1th Parameter |                     |                     |                     |                     |                     |                     |         | The 1st byte read is dummy byte. The 2nd byte read is the content of Address 0 in OTP The N+1th byte read is the content of Address n in OTP After issue this command, the host must read at least 1 byte data from the device.                                                     |

|      | 0  | F0  | 4                   |                                                              |                     | _                   |                     |                     | 4                   | 4                   | DWC     | Davian Carling Daviates                                                                                                                                                                                                                                                             |

| 0    | 1  | E3  | 1<br>A <sub>7</sub> | 1<br>A <sub>6</sub>                                          | 1<br>A <sub>5</sub> | 0<br>A <sub>4</sub> | 0<br>A <sub>3</sub> | 0<br>A <sub>2</sub> | 1<br>A <sub>1</sub> | 1<br>A <sub>0</sub> | PWS     | Power Saving Register This command is sets for saving power VCOM/Source power saving during display refresh period. A[7:0] = 65h [POR]                                                                                                                                              |

SSD2677 Product Info

Rev 1.1

P 11/19

Aug 2023

Solomon Systech

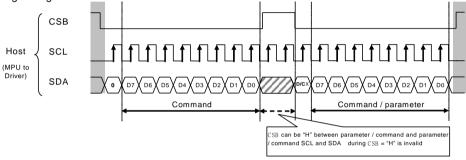

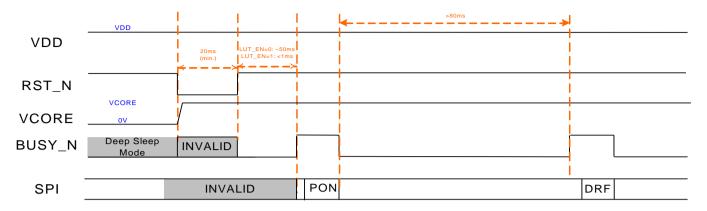

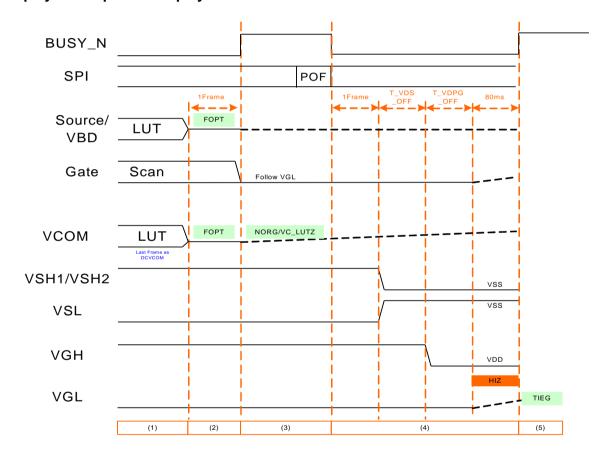

## 6 Display on/off Sequence

## 6.1 Display on sequence from VDD power on

### 6.2 Display on sequence from deep sleep mode

### 6.3 Display off Sequence Display

### 7 Absolute Maximum Rating

**Table 7-1: Maximum Ratings**

| Symbol           | Parameter                   | Rating                         | Unit |

|------------------|-----------------------------|--------------------------------|------|

| $V_{DD}$         | Logic supply voltage        | -0.5 to +4.0                   | V    |

| VIN              | Logic Input voltage         | -0.5 to V <sub>DDIO</sub> +0.5 | V    |

| Vouт             | Logic Output voltage        | -0.5 to V <sub>DDIO</sub> +0.5 | V    |

| Topr             | Operation temperature range | -30 to +85                     | °C   |

| T <sub>STG</sub> | Storage temperature range   | -65 to +150                    | °C   |

Maximum ratings are those values beyond which damages to the device may occur. Functional operation should be restricted to the limits in the Electrical Characteristics tables or Pin Description section

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that VDD be constrained to the range GND < VDD. Reliability of operation is enhanced if unused input is connected to an appropriate logic voltage level (e.g., either GND or  $V_{\text{DDIO}}$ ). Unused outputs must be left open. This device may be light sensitive. Caution should be taken to avoid exposure of this device to any light source during normal operation. This device is not radiation protected.

### 8 Electrical Characteristics

The following specifications apply for: GND=0V, VDD=3.0V, T<sub>OPR</sub>=25°C.

**Table 8-1: DC Characteristics**

| Symbol               | Parameter                          | Applicable pin                  | Test Condition | Min.                 | Тур.                | Max.                 | Unit |

|----------------------|------------------------------------|---------------------------------|----------------|----------------------|---------------------|----------------------|------|

| V <sub>DD</sub>      | VDD supply operation voltage       | VDD                             |                | 2.3                  | 3.0                 | 3.6                  | V    |

| Vcom_dc              | VCOM_DC output voltage             | VCOM                            |                | -4.0                 | -                   | -0.2                 | V    |

| dV <sub>COM_DC</sub> | VCOM_DC output voltage deviation   | VCOM                            | No output load | -200                 | -                   | 200                  | mV   |

| Vcom_ac              | VCOM_AC output voltage             | VCOM                            |                | VsL                  | V <sub>СОМ_DС</sub> | VsH                  | V    |

| V <sub>GATE</sub>    | Gate output voltage                | G0~G679                         |                | -20                  | -                   | +20                  | V    |

| VGATE(p-p)           | Gate output peak to peak voltage   | G0~G679                         |                | -                    | -                   | 40                   | V    |

| VSH                  | Positive Source output voltage     | VSH1                            |                | +3                   |                     | +15                  | V    |

| VSH2                 | Positive Source output voltage     | VSH2                            |                | +3                   |                     | +15                  | V    |

| dVsн                 | VSH1/VSH2 output voltage deviation | VSH1/ VSH2                      | No output load | -200                 | -                   | 200                  | mV   |

| VsL                  | Negative Source output voltage     | VSL                             |                | -15                  |                     | -3                   | V    |

| dV <sub>SL</sub>     | VSL output voltage deviation       | VSL                             | No output load | -200                 | -                   | 200                  | mV   |

| ViH                  | High level input voltage           | SDA SCL, CSB, DC,<br>RST_N, BS1 |                | 0.8V <sub>DDIO</sub> | -                   | -                    | V    |

| VIL                  | Low level input voltage            |                                 |                | -                    | -                   | 0.2V <sub>DDIO</sub> | V    |

| V <sub>OH</sub>      | High level output voltage          | SDA, BUSY_N,                    | IOH = -100uA   | 0.8V <sub>DDIO</sub> | -                   | -                    | V    |

| Vol                  | Low level output voltage           | <u> </u>                        | IOL = 100uA    | -                    | -                   | 0.2V <sub>DDIO</sub> | V    |

| SSD2677      | Dov 1.1 | D 44/40 | Aug 2023 | Salaman Suatach |

|--------------|---------|---------|----------|-----------------|

| Product Info | Rev 1.1 | P 14/19 | Aug 2023 | Solomon Systech |

| Symbol           | Parameter                     | Applicable pin | Test Condition                                                                             | Min.  | Тур. | Max.  | Unit |

|------------------|-------------------------------|----------------|--------------------------------------------------------------------------------------------|-------|------|-------|------|

| V <sub>PP</sub>  | OTP Program voltage           | VPP            |                                                                                            | 8.1   | 8.3  | 8.5   | V    |

| Islp_VDD         | Sleep mode current            | VDD            | - DC/DC off - No clock - No output load - MCU interface access - RAM data access           | -     | TBD  | TBD   | uA   |

| Idslp_VDD        | deep sleep current            | VDD            | - DC/DC off - No clock - No output load - No MCU interface access - Cannot retain RAM data | -     | TBD  | TBD   | uA   |

| lopr_VDD         | Operating Mode current        | VDD            | VDD=3V                                                                                     | -     | TBD  | -     | mA   |

| V <sub>GH</sub>  | Operating Mode Output Voltage | VGH            | After PON<br>Command                                                                       | 19.5  | 20   | 20.5  | V    |

| V <sub>SH</sub>  |                               | VSH1           | VGH=20V<br>VGL=-VGH<br>                                                                    | 14.8  | 15   | 15.2  | V    |

| V <sub>SH2</sub> |                               | VSH2           | VSH2=15V<br>VSL=-15V                                                                       | 14.8  | 15   | 15.2  | V    |

| V <sub>SL</sub>  |                               | VSL            | VCOM = -2V<br>No waveform                                                                  | -15.2 | -15  | -14.8 | V    |

| Vсом             |                               | VCOM           | transitions. No output load No RAM read/write                                              | -2.2  | -2   | -1.8  | V    |

SSD2677 Product Info

Rev 1.1

P 15/19

Aug 2023

Solomon Systech

### 9 AC Characteristics

### 9.1 Serial Peripheral Interface

The following specifications apply for: VDDIO - GND = 2.3V to 3.6V, T<sub>OPR</sub> = 25°C, CL=20pF

**Table 9-1: Serial Peripheral Interface Timing Characteristics**

| Symbol           | Parameter                   | Min | Тур | Max | Unit |

|------------------|-----------------------------|-----|-----|-----|------|

| tcss             | CSB select setup time       | TBD |     |     | ns   |

| tsc <sub>H</sub> | CSB select hold time        | TBD |     |     | ns   |

| tscc             | CSB deselect setup time     | TBD |     |     | ns   |

| t <sub>CHW</sub> | CSB deselect hold time      | TBD |     |     | ns   |

| tscycw           | Serial clock cycle (Write)  | TBD |     |     | ns   |

| t <sub>SHW</sub> | SCL "H" pulse width (Write) | TBD |     |     | ns   |

| tslw             | SCL "L" pulse width (Write) | TBD |     |     | ns   |

| tscycl           | Serial clock cycle (Read)   | TBD |     |     | ns   |

| t <sub>SHR</sub> | SCL "H" pulse width (Read)  | TBD |     |     | ns   |

| tslr             | SCL "L" pulse width (Read)  | TBD |     |     | ns   |

| t <sub>SDS</sub> | Data setup time             | TBD |     |     | ns   |

| t <sub>SDH</sub> | Data hold time              | TBD |     |     | ns   |

| tacc             | Access time                 |     |     | TBD | ns   |

| tон              | Output disable time         | TBD |     |     | ns   |

Note: All timings are based on 20% to 80% of VDDIO-GND

Figure 9-1: 3-wire serial interface characteristics (write mode)

Figure 9-2: 3-wire serial interface characteristics (read mode)

SSD2677 products shall only be used solely with Permitted E5 Spectra 3100 FPL licensed by E Ink, customer should notify the same acknowledgement with its downstream customers.

SSD2677 Product Info

Rev 1.1

P 16/19

Aug 2023

Solomon Systech

Figure 9-3: 4-wire pin serial interface characteristics (write mode)

Figure 9-4: 4-wire serial interface characteristics (read mode)

SSD2677 Product Info

Rev 1.1

P 17/19

Aug 2023

Solomon Systech

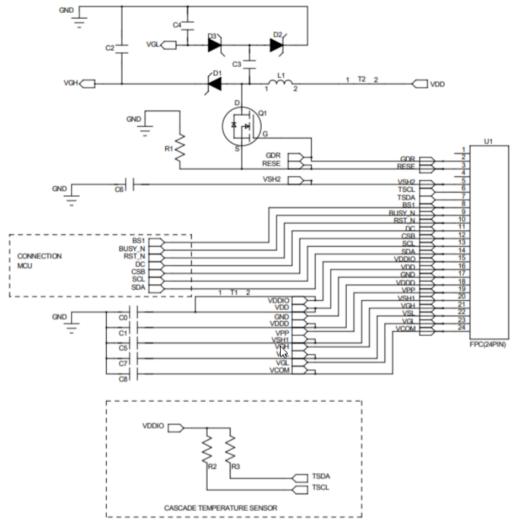

# 10 Application Circuit

Figure 10-1: SSD2677 application circuit

Table 10-1: Component list for SSD2677 application circuit

| Part Name | Value            | Requirements/Reference Part                                                                                                    |  |

|-----------|------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| C0        | 4.7uF            | X5R/X7R; Voltage Rating : 6V or 25V                                                                                            |  |

| C1        | 1uF              | X5R/X7R; Voltage Rating : 6V or 25V                                                                                            |  |

| C2-C7     | 4.7uF            | 0805; X5R/X7R; Voltage Rating: 25V                                                                                             |  |

| C8        | 1uF              | 0805; X7R; Voltage Rating: 25V                                                                                                 |  |

| R1        | 2.2 ohm          | 0805; 1%                                                                                                                       |  |

| R2, R3    | Open             | Connect to VSS in single chip application                                                                                      |  |

| D1-D3     | Diode            | MBR0530 1) Reverse DC voltage ≥ 30V 2) Io ≥ 500mA 3) Forward voltage ≤ 430mV                                                   |  |

| Q1        | NMOS             | Si1304BDL/NX3008NBK  1) Drain-Source breakdown voltage ≤ 30V 2) Vgs(th) = 0.9V (Typ), 1.3V (Max) 3) Rds on ≤ 2.1Ω @ Vgs = 2.5V |  |

| L1        | 47uH             | CDRH2D18 / LDNP-470NC<br>Io= 500mA (Max)                                                                                       |  |

| U1        | 0.5mm ZIF socket | 24pins, 0.5mm pitch                                                                                                            |  |

### Remarks:

- 1) The recommended component value and reference part in Table 10-1 is subject to change depending on panel loading.

- 2) Customer is required to review if the selected component value and part is suitable for their application.

| SSD2677      | David 4 | P 18/19 | A 2022   | Calaman Custock |

|--------------|---------|---------|----------|-----------------|

| Droduct Info | Rev 1.1 | P 16/19 | Aug 2023 | Solomon Systech |

Solomon Systech reserves the right to make changes without notice to any products herein. Solomon Systech makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Solomon Systech assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any, and all, liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typical" must be validated for each customer application by the customer's technical experts. Solomon Systech does not convey any license under its patent rights nor the rights of others. Solomon Systech products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Solomon Systech product could create a situation where personal injury or death may occur. Should Buyer purchase or use Solomon Systech products for any such unintended or unauthorized application, Buyer shall indemnify and hold Solomon Systech and its offices, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Solomon Systech was negligent regarding the design or manufacture of the part.

The product(s) listed in this datasheet comply with Directive (EU) 2015/863 of 31 March 2015 amending Annex II to Directive 2011/65/EU of the European Parliament and of the Council as regards the list of restricted substances and People's Republic of China Electronic Industry Standard GB/T 26572-2011 "Requirements for concentration limits for certain hazardous substances in electronic information products (电子电器产品中限用物質的限用要求)". Hazardous Substances test report is available upon request.

http://www.solomon-systech.com

SSD2677 products shall only be used solely with Permitted E5 Spectra 3100 FPL licensed by E Ink, customer should notify the same acknowledgement with its downstream customers.

SSD2677 Product Info

Rev 1.1

P 19/19

Aug 2023

Solomon Systech